本文共 3470 字,大约阅读时间需要 11 分钟。

4.存储器

4.2.1概述

主存的技术指标:

-

存储容量:能存放二进制代码的总位数

存储容量 = 存储单元个数 x 存储字长 例如:存储字长32位 = 4字节,存储容量=4*32=128MB -

存储速度

- 存储时间

- 读出时间:从存储器接收有效地址开始,到产生有效输出所需要的全部时间

- 写入时间:从存储器接收有效地址开始,到数据写入被选中单元所需要的全部时间

- 存储周期:两次独立的存储操作所需要的最小间隔(存储周期大于存储时间)

- 存储时间

-

存储器带宽

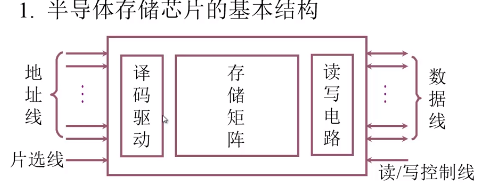

4.2.2半导体存储芯片简介

半导体存储芯片的译码驱动方式:

地址线:10根,数据线为4根, 芯片容量 :210 x 4 = 4k位

- 线选法

A0,A1,A2,A3,有4位地址线,有24根(16根)地址线,1根数据线,上图是16 X 1字节线选法存储芯片结构图

A0,A1,A2,A3,有4位地址线,有24根(16根)地址线,1根数据线,上图是16 X 1字节线选法存储芯片结构图

存在问题:

假设1M *8的存储器,20位地址线,有220次方,也就是100万条线,内存很难集成这么高,那么新的方法来了。。。。

- 重合法 线选法把存储单元布置为一维数组,重合法把存储单元布置为二维数组

差异: 20位地址线,x方向10位,有210(1k条),y方向10位,有210(1k条),总共需要2k条线,比上述的线选法1M条线,节省太多

差异: 20位地址线,x方向10位,有210(1k条),y方向10位,有210(1k条),总共需要2k条线,比上述的线选法1M条线,节省太多

4.2.3随机存取存储器(RAM)

静态RAM

保存0与1的原理:利用触发器工作原理存储信息

一般有一个输出端和两个输入端(“+”、“-”端各一个),当输入端的“+”端有触发信号时,输出端不管原来是什么状态,都会立即变为高电平,且一直稳定地输出高电平。如果当输入端的“-”端有触发信号时,输出端不管原来是什么状态,都会立即变为低电平,且一直稳定地输出低电平。这就是双稳态电路。

读操作:

写操作:

动态RAM

保存0与1的原理:DRAM使用电容存储,电荷维持1~2ms,所以必须隔一段时间刷新(refresh)一次,如果存储单元没有被刷新,存储的信息就会丢失。 关机就会丢失数据。

高电容表示存1

低电容表示存0

三管式动态RAM

读操作

1.T4管放置预充电信号,读数据线达到高电平Vdd

2.读数据线打开T2 3.如果极间电容Cg原存“1”(高电荷),T1导通,因为T2,T1导通后接地,读数据线电平降为(低电荷)读出“0” 4.如果极间电容Cg原存“0”(低电荷),T1截止,读数据线电平不变 读出“1” 5.读出线因为电平改变,读出信息与原信息相反写操作

1.写数据线有效 T3管导通

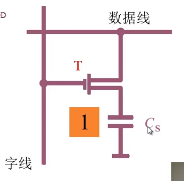

2.如果写入数据为1,写数据线为高电平,通过T3向Cg进行充电,Cg中保存1 3.如果写入数据为0,写数据线为低电平,通过T3向Cg进行放电,Cg中保存0 4.写入信息与输入信息完全相同单管动态RAM

读操作

1.字线上的高电平使T打开,

2.如果Cs上保存“1”为高电荷,经过T管在数据线上产生高电流,可以视为读出“1” 3.如果Cs上保存“0”为高电荷,经过T管在数据线上产生低电流,可以视为读出“0”写操作

1.子线为高电平使T管导通,

2.如果写入“1”,数据线为高电平,经过T管对Cs充电,使其存“1” 3.如果写入“0”,数据线为低电平,经过T管对Cs放电,使其无电荷存“0”动态RAM刷新

刷新实质:先将原存信息读出,再有刷新放大器形成原信息并且重新写入的再生过程

与行地址有关

1)集中刷新

2)分散刷新

3)异步刷新

4.2.5 存储器与cpu的连接

1.存储容量的扩展

存储芯片容量有限,必须将若干存储芯片连在一起才能组成足够容量的存储器,通常有:

- 位扩展

- 字扩展

- 字 位同时扩展

位扩展:

2片1K x 4位 存储芯片怎么组成1k x 8位的存储芯片?

同时扩展: 8片1K x 4位 存储芯片怎么组成4k x 8位的存储芯片?

同时扩展: 8片1K x 4位 存储芯片怎么组成4k x 8位的存储芯片?

2.存储器与cpu的连接

1)地址线的连接

cpu的地址线比存储芯片的地址线多,通常是将cpu地址线的低位与存储芯片的地址线连接,高位扩充使用 2)数据线的连接 3)读写命令线的连接 高电平读 低电平写 4)片选线的连接(关键) 如果cpu没有访问存储器访问了I/O,来自CPU的片选有效信号MREQ为高电平,表示不要求存储器工作 5)合理选择存储芯片 ROM存放系统程序 RAM存放用户信息4.2.6存储器的校验

设欲检测的二进制代码为n位,为使其具有纠错能力,需要添加K位检测位,组成n+k位的代码,检测位数K 应该满足 2k>= n+ k +1

检测位编号为:1 2 4 8 … 2k-1 c1 检测的小组包含1 3 5 7 9 11 。。。位 c2 检测的小组包含2 3 6 7 10 11 14 15 。。。位 c4 检测的小组包含4 5 6 7 12 13 14 15 。。。位4.2.6提高访存速度的措施

存储器模块数为:n,存取周期为:T 总线传输周期:t 已知低位交叉的存储器,连续读取n个字所需要的时间t1为: T +(n-1)t

已知高位交叉的存储器,连续读取n个字所需要的时间t2为: nT

单体多字系统:

适用于程序和数据在存储体内是连续存放的情况。在一个存取周期内,从同一地址取出多条指令,然后再逐条将指令送至CPU执行,这样增大了存储器的带宽,提高了单体存储器的速度。这里的单体应该就是一个模块,但是每次可以读取多个字,可以和多体进行比较。 多体并行系统 有多个模块,每个模块有相同的容量以及存取速度,各模块各自都有独立的地址寄存器(MAR),数据寄存器(MDR),地址译码,驱动电路和读写电路,他们能够并行工作,同时也能交叉工作(什么是交叉工作?),但是并行读出的数据在总线上需要分时传送。 地址分为体号与体内地址。 对于高位交叉编址的多体存储器而言,程序按体内地址顺序存放,他们在每一个模块中的地址是连续的,有利于存储器的扩充。高位地址表示体号,低位地址表示体内地址。对于低位交叉编址的多体存储器而言,程序连续存放在相邻体中(又有交叉存储之称),低位地址表示体号,高位地址表示体内地址。这种编址方式又称为模M编址,其中M为模块数。

每个模块的存取周期是不变的,但是CPU交叉访问各体,使得这几个存储体的读/写过程重叠进行。对于低位交叉的存储器,连续读取n个字所需的时间为T+(n-1)t, 对于高位交叉的存储器,连续读取n个字所需的时间为nT,

4.3高速缓冲存储器

背景:I/o设备向主存请求的级别高于cpu访存,出现了cpu等待I/o设备访存的现象,致使cpu空等一段时间,降低了工作效率;cache的出现让cpu可以不直接访问主存,而与高速cache交换信息

程序访问的局部性:cpu从主存中存取指令的数据,只对主存局部区域地址访问,这是由于指令和数据在主存内都是连续存放的,使得cpu在执行程序中,访存具有相对局部性,这就称为程序访问的局部性; 公式:- 一:h:命中率,Nc访问cache总命中次数,Nm访问主存的总次数 h = Nc / Nc + Nm

- 二:ta = Cache -主存系统的平均访问时间 tc为:命中时的cache访问时间,tm为未命中时的主存访问时间,1-h:未命中率 ta = h tc + (1-h) tm

- 三 e:访问效率 tc:命中时的cache访问时间 ta: Cache -主存系统的平均访问时间 e=tc / ta * 100%

4.32.cache -主存地址映射

转载地址:http://qothn.baihongyu.com/